# EL Amplificador Operacional de Transconductancia de Miller en tecnología CMOS

## Enrique Alonso, torpedix@hotmail.com Javier Valcarce, javier.valcarce@gmail.com

## 25 de mayo de 2006

## Índice

| 1. | El OTA-Miller                                                |  |  |  |  |  |  |

|----|--------------------------------------------------------------|--|--|--|--|--|--|

| 2. | Estudio teórico                                              |  |  |  |  |  |  |

|    | 2.1. Dimensionamiento del transistor TF                      |  |  |  |  |  |  |

|    | 2.2. Puntos de polarización                                  |  |  |  |  |  |  |

|    | 2.3. Ganancia                                                |  |  |  |  |  |  |

|    | 2.4. Excursión de salida                                     |  |  |  |  |  |  |

| 3. | Simulación de la descripción eléctrica                       |  |  |  |  |  |  |

|    | 3.1. Puntos de polarización                                  |  |  |  |  |  |  |

|    | 3.2. Ganancia y ancho de banda, excursión y offset de salida |  |  |  |  |  |  |

| 4. | Simulación de la descripción física                          |  |  |  |  |  |  |

|    | 4.1. Simulación física del bloque FUENTE                     |  |  |  |  |  |  |

|    | 4.2. Simulación física del bloque PARDIF                     |  |  |  |  |  |  |

|    | 4.3. Simulación física del bloque SALIDA                     |  |  |  |  |  |  |

|    | 4.4. Simulación física del layout                            |  |  |  |  |  |  |

| Δ  | Estudio de una fuente de corriente CMOS                      |  |  |  |  |  |  |

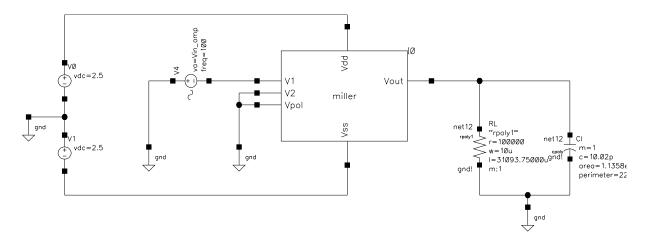

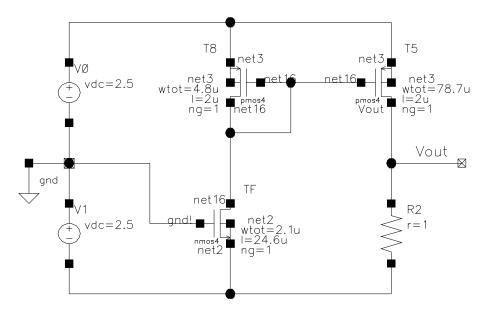

Figura 1: Esquema para simular el diseño

## 1. El OTA-Miller

Los amplificadores operacionales de transconductancia (OTA) son amplificadores operacionales cuya salida, en lugar de ser una fuente de tensión de baja impedancia como en los amplificadores operacionales convencionales, es una fuente de corriente de alta impedancia controlada mediante la tension diferencial de entrada. En este trabajo de clase simulamos la descripción eléctrica y física de un OTA de Miller en tecnología CMOS, su estructura puede verse en la Figura 2. El esquema de la Figura 1 se usa para simulación.

## 2. Estudio teórico

#### 2.1. Dimensionamiento del transistor TF

Todos los transistores MOS del circuito deben estar saturados, en este modo  $V_{gs} - V_{th} < V_{ds}$  y su corriente es

$$I_d = K (V_{gs} - V_{th})^2 [1 + \lambda V_{ds}]$$

(1)

donde asumimos  $\lambda=0$  (no hay efecto de modulación de la longitud del canal) para todos los cáculos que vienen a continuación.

Queremos dimensionar el trasistor  $T_F$  ( $V_{pol}$ ,  $W_F$  y  $L_F$ ) exigiendo que la corriente de referencia  $I_{ref}$  sea 7.05uA. Lo primero es calcular los márgenes admisibles para  $V_{pol}$ . El transistor  $T_F$  no puede estar en corte

$$V_{gsF} > V_{thF}$$

$$V_{pol} - V_{ss} > V_{thF}$$

$$V_{pol} > -1.74 \text{V}$$

además, debe estar saturado

$$V_{gsF} - V_{thF} < V_{dsF}$$

$$V_{pol} - V_{ss} - V_{thF} < V_{dsF}$$

$$V_{dsF} = V_{dd} - V_{ss} - |V_{ds8}|$$

despejando  $V_{qs}$  en (1), la tensión  $V_{ds8}$  es

$$|V_{ds8}| = |V_{gs8}| = \sqrt{\frac{|I_{d8}|}{K_p'} \frac{L_8}{W_8}} + |V_{th8}|$$

(2)

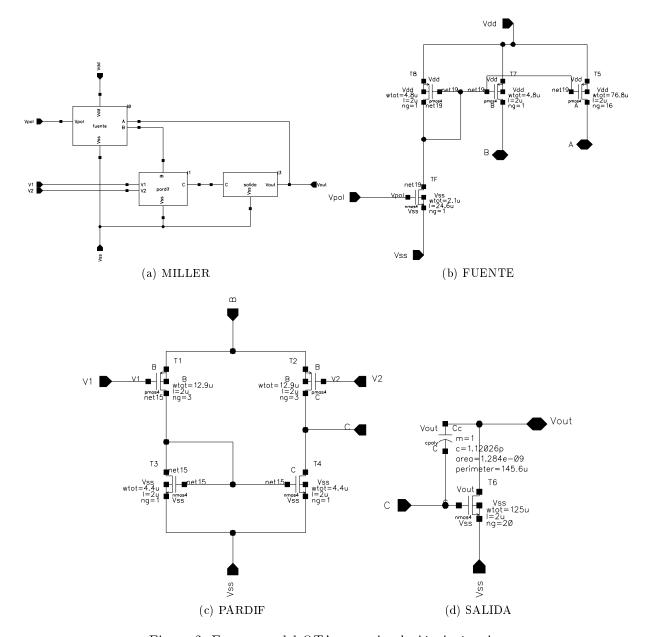

Figura 2: Esquemas del OTA para simulación jerárquica

si exigimos que la corriente  $I_{ref}=|I_{d8}|=7.05$ u<br/>A entonces  $|V_{ds8}|=1.2624$ V y el límite superior para  $V_{pol}$  es 1.9976<br/>V. En resumen

$$-1.74V < V_{pol} < 1.9976V (3)$$

Conociendo el rango admisible de  $V_{pol}$ , podemos fijarlo a un valor concreto y despejar la relación de aspecto  $(W/L)_F$ . Fijando el valor central  $V_{pol}=0$

$$\left(\frac{W}{L}\right)_F = \frac{I_{ref}}{K_n'(-V_{qsF} - V_{thF})} = 0.071$$

fijando<br/>1 $W_F=2\mathrm{um}$ tenemos una  $L_F=W_F/0.071=28.17\mathrm{um}.$  Estas dimensiones son efectivas, las dibujadas son

$$W_{dibF} = W_F - 2WD_n = 2.1$$

um

$L_{dibF} = L_F - 2LD_n = 28$ um

$<sup>^1{\</sup>rm Si}$  fijamos  $L_F=2{

m um}$  obtenemos  $W_F=0.142{

m um}$  que es un valor imposible para esta tecnología

#### 2.2. Puntos de polarización

Primero calculamos la  $I_d$  y  $V_{gs}$  de todos los transistores. A partir de la  $I_d$ , la  $V_{gs}$  se obtiene despejando en la ecuación (1)

$$V_{gs} = \sqrt{\frac{I_d}{K} \frac{L}{W}} + V_{th} \tag{4}$$

donde L y W son siempre dimensiones efectivas y poniendo el signo, la constante K y  $V_{th}$  correcta dependiendo de si es un transistor nMOS o pMOS

$$I_{dF} = 7.05 \text{uA} \longrightarrow V_{gsF} = +2.4540 \text{V}$$

$I_{d8} = I_{dF} \longrightarrow V_{gs8} = -1.2624 \text{V}$

los transistores  $T_7$  y  $T_5$  copian la corriente de referencia multiplicandola de forma proporcional a su relación areas

$$\begin{split} I_{d7} &= [(W/L)_7/(W/L)_8] I_{dF} = 007.05 \text{uA} \longrightarrow V_{gs7} = -1.2624 \text{V} \\ I_{d5} &= [(W/L)_5/(W/L)_8] I_{dF} = 115.60 \text{uA} \longrightarrow V_{gs5} = -1.2524 \text{V} \\ I_{d6} &= I_{d5} \longrightarrow V_{gs6} = +0.9931 \text{V} \end{split}$$

con  $V_1 = 0$ V y  $V_2 = 0$ V el par difencial está en equilibrio y la corriente por cada una de sus ramas es la mitad de la que viene de la fuente de corriente  $T_7$

$$\begin{split} I_{d1} &= I_{d7}/2 = 3.525 \text{uA} \longrightarrow V_{gs1} = -0.9881 \text{V} \\ I_{d3} &= I_{d1} \longrightarrow V_{gs3} = +0.9703 \text{V} \\ I_{d2} &= I_{d7}/2 = 3.525 \text{uA} \longrightarrow V_{gs2} = -0.9881 \text{V} \\ I_{d4} &= I_{d2} \longrightarrow V_{gs4} = +0.9703 \text{V} \end{split}$$

La tensión  $V_{ds}$  de los transistores la podemos obtener a partir de las tensiones  $V_{qs}$ ,  $V_{dd}$  y  $V_{ss}$

$$\begin{split} V_{dsF} &= V_{dd} + V_{gs8} - V_{ss} = +3.7376 \text{V} \\ V_{ds8} &= V_{gs8} = -1.2624 \text{V} \\ V_{ds6} &= V_{dsF} - V_{gs5} = +2.4852 \text{V} \\ V_{ds5} &= -(V_{dd} - V_{ss} - V_{ds6}) = -2.5158 \text{V} \\ V_{ds1} &= V_{dsF} + V_{gs7} - V_{ds3} = -2.5180 \text{V} \\ V_{ds2} &= V_{ds1} + V_{gs4} - V_{ds4} = -2.4950 \text{V} \\ V_{ds3} &= V_{gs4} = +0.9703 \text{V} \\ V_{ds4} &= V_{gs6} = +0.9931 \text{V} \\ V_{ds7} &= V_{dd} + V_{ds1} - V_{ds3} - V_{ss} = -1.5120 \text{V} \end{split}$$

Los cálculos de  $V_{qs}$  los hemos realizado con el siguiente script para Octave:

```

% [Vgs] = mospol(type, Id, W, L)

function [Vgs] = mospol(type, Id, W, L)

Weff = W - 2*(-50e-9);

Leff = L - 2*(+75e-9);

Kn = 32.780e-6; Vthn = 0.76;

Kp = 12.625e-6; Vthp = 0.78;

```

| Transistor | $g_m \text{ (uS)}$ | $g_{ds}$ (uMHO) |

|------------|--------------------|-----------------|

| T1         | 33.88              |                 |

| T2         |                    | 0.147           |

| Т3         |                    |                 |

| T4         |                    | 0.1             |

| T5         |                    | 4.816           |

| Т6         | 991.93             | 3.288           |

Cuadro 1: Transconductancia y admitancia de los transistores del circuito

```

if type == 'n'

Vgs = sqrt(Id/Kn*Leff/Weff) + Vthn;

elseif type == 'p'

% Vgs en módulo, WD,LD=0

Vgs = -(sqrt(Id/Kp*L/W) + Vthp);

else

Vgs = NaN;

end

```

#### 2.3. Ganancia

Usando el modelo de pequeña señal del OTA Miller, la expresión para la ganancia es  $A_v = A_{v1}A_{v2}$  con  $A_{v1}$  y  $A_{v2}$  la ganancia de la etapa diferencial y la de salida respectivamente. Ambas dependen de las transconductancias  $(g_{mi})$  y admitancias de salida  $(g_{dsi})$  de los transistores  $T_i$  del circuito así como de la resistencia de carga  $R_L$ . En la Tabla 1 aparecen sólo los parámetros que son necesarios para calcular la ganancia, sus expresiones son

$$g_{mi} = 2\sqrt{K'\frac{W}{L}I_{di}} \tag{5}$$

$$g_{dsi} = \frac{I_{di}}{V_F L_i} \tag{6}$$

la ganancia de la 1º etapa (par diferencial) es

$$A_{v1} = \frac{g_{m1}}{g_{ds2} + g_{ds4}} = \frac{33.88}{0.147 + 0.1} = 137.16 \tag{7}$$

la ganancia de la 2º etapa (inversor CMOS) es

$$A_{v2} = \frac{g_{m6}}{1/R_L + g_{ds5} + g_{ds6}} = 54.790 \tag{8}$$

y la ganancia total del amplificador es entonces

$$|A_v| = |A_{v1}| |A_{v2}| = 137.16 \cdot 54.79 = 7514.99 \tag{9}$$

$$20log(A_v) = 77.52dB \tag{10}$$

que es un valor parecido al obtenido por simulación.

#### 2.4. Excursión de salida

La señal de salida comienza a distorsionarse cuando  $T_5$  y  $T_6$  dejan de estar en saturación, por lo que la excursión de salida no es  $\pm 2.5$ V, sino un poco menor. El transistor  $T_5$  estará en el límite de saturación cuando

$$|V_{ds5}| = |V_{ds5min}| = |V_{as5} - V_{th5}| = 0.482$$

V

en ese momento  $V_{out} = V_{dd} - |V_{ds5min}| = 2.018 \text{V}$  y esa es precisamente la amplitud en la que  $V_{out}$  se distorsiona y es la excursión máxima en salida positiva. Lo mismo ocurre con  $T_6$  cuando  $V_{out}$  es negativa, en ese caso la excursión máxima en negativa es  $V_{out} = V_{ss} + (V_{gs6} - V_{th6}) = -2.2669 \text{V}$

## 3. Simulación de la descripción eléctrica

#### 3.1. Puntos de polarización

Al ejecutar la herramienta Analog Environment para simular el esquema eléctrico le podemos decir que nos muestre los puntos de polarización de los transistores calculados durante el análisis transitorio (Results  $\rightarrow$  Print  $\rightarrow$  Transient Operating Points).

Vemos que la corriente  $I_b$  no exactamente 7.05uA sino 6.196uA, así que ajustamos el transistor  $T_F$  ya calculado disminuyendo su longitud de L=28um a L'=24.6um y volvemos a simular, ahora la corriente  $I_b$  ya es correcta.

En la Tabla 2 se comparan los puntos de polarización teóricos con los que nos da la herramienta (tomando siempre valor absoluto).

|            | Teórico       |                        |                        | Simulación    |                        |                        |

|------------|---------------|------------------------|------------------------|---------------|------------------------|------------------------|

| Transistor | $I_{ds}$ (uA) | $V_{ds} (\mathrm{mV})$ | $V_{gs} (\mathrm{mV})$ | $I_{ds}$ (uA) | $V_{ds} (\mathrm{mV})$ | $V_{gs} (\mathrm{mV})$ |

| T1         | 3.525         | 2.5180                 | 0.9881                 | 3.534         | 2.574                  | 1.057                  |

| T2         | 3.525         | 2.4950                 | 0.9881                 | 3.533         | 2.574                  | 1.057                  |

| T3         | 3.525         | 0.9703                 | 0.9703                 | 3.534         | 0.983                  | 0.983                  |

| T4         | 3.525         | 0.9931                 | 0.9703                 | 3.534         | 0.983                  | 0.983                  |

| T5         | 115.60        | 2.5000                 | 1.2524                 | 145.1         | 2.527                  | 1.386                  |

| Т6         | 115.60        | 2.4852                 | 0.9931                 | 145.7         | 2.433                  | 0.983                  |

| T7         | 7.05          | 1.5120                 | 1.2624                 | 7.067         | 1.433                  | 1.386                  |

| T8         | 7.05          | 1.2624                 | 1.2624                 | 7.055         | 1.386                  | 1.386                  |

| TF         | 7.05          | 3.7376                 | 2.4100                 | 7.055         | 3.614                  | 2.500                  |

Cuadro 2: Polarización del circuito teórica y por simulación

#### 3.2. Ganancia y ancho de banda, excursión y offset de salida

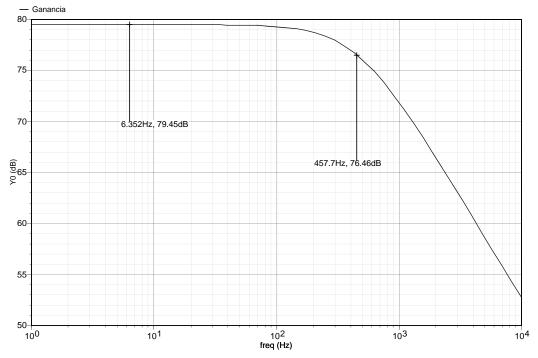

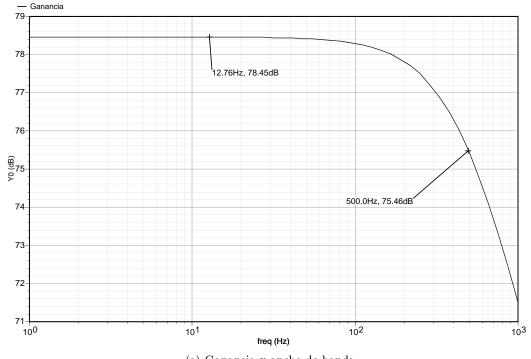

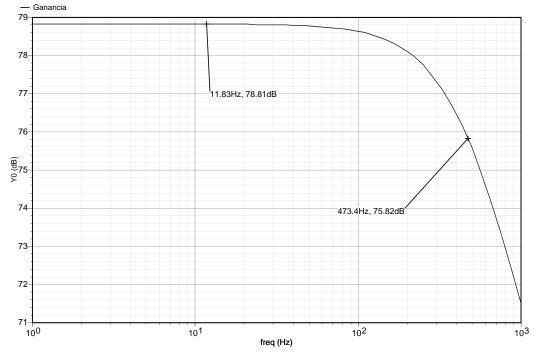

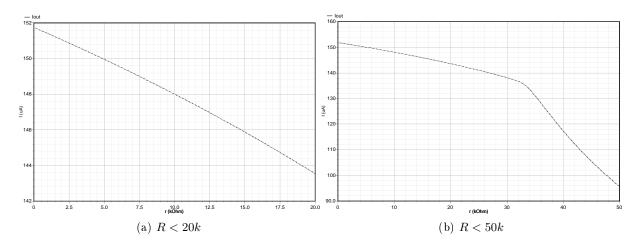

En la Figura 3 se puede ver la función de tranferencia, el producto  $G \times BW$  calculado usando la función gainBwProd sobre la curva en la calculadora del Analog Environement es 4.207M

## 4. Simulación de la descripción física

En este apartado del trabajo dibujamos el layout de cada uno de los tres bloques FUENTE, PAR-DIF y SALIDA, y comprobamos que pasan el DRC y el LVS. Desde la vista Extracted de cada uno hacemos Verify  $\rightarrow$  LVS  $\rightarrow$  Build Analog para obtener un modelo de simulación con las características físicas del layout (analog extracted).

Con el editor de jerarquía sustituimos estos modelos en el esquema de bloques MILLER de uno en uno cada vez y volvemos a simular.

Al hacer la sustitución de la fuente (bloque FUENTE) hemos visto que el offset de salida era muy elevado (315mV aprox) con este nuevo modelo, así que hemos aumentado la W de T6 de W=120um a W'=125um para que circule más corriente a través y baje así el offset de salida.

Los resultados de las tres simulaciones se muestran en los respectivos apartados siguientes, siempre con T6 ya corregido.

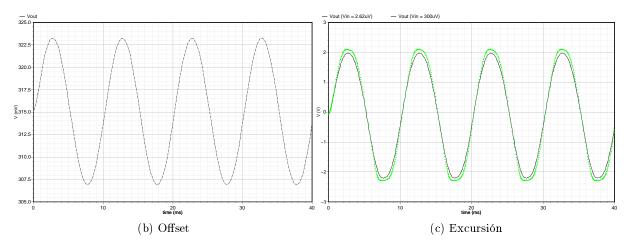

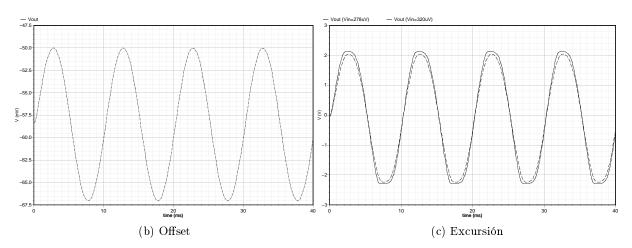

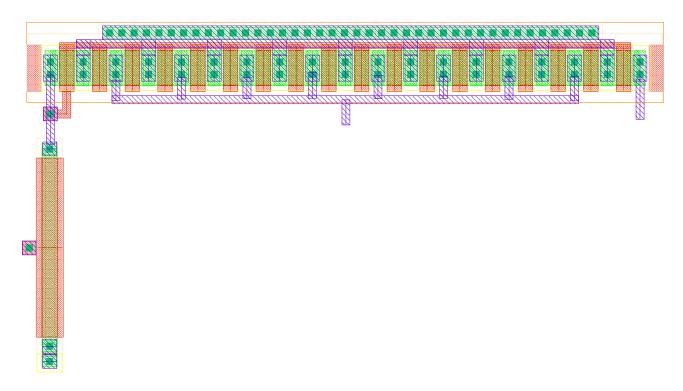

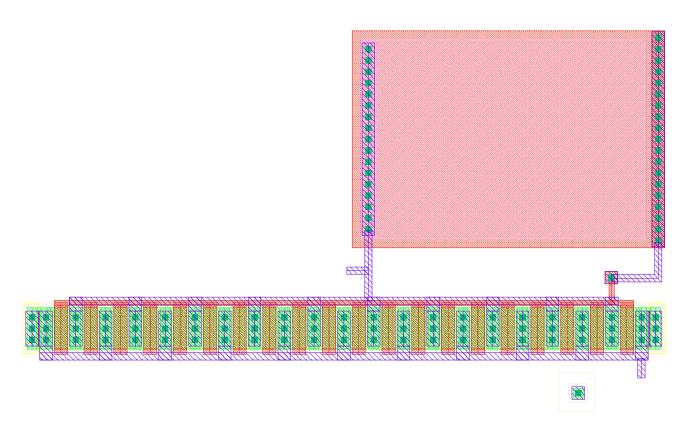

#### 4.1. Simulación física del bloque FUENTE

El layout de este bloque se muestra en la Figura 10 y los resultados de los análisis en alterna y transitorio en la Figura 4. La descomposición en transistores unitarios (TUs) es la siguiente:

Figura 3: Simulación de la descripción eléctrica

- T7 mide 4.8um, 01 TUs de 4.8um

- T8 mide 4.8um, 01 TUs

- T5 mide 120um, 16 TUs

Los transistores unitarios de T5 están dispuestos en el centro y T7 y T8 a los lados buscando una estructura lo más homogenea y regular posible.

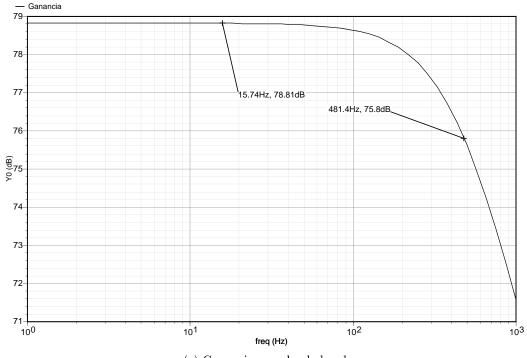

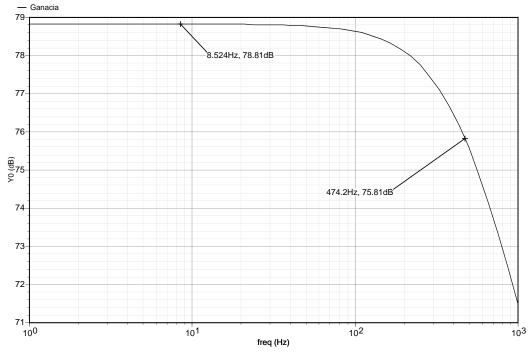

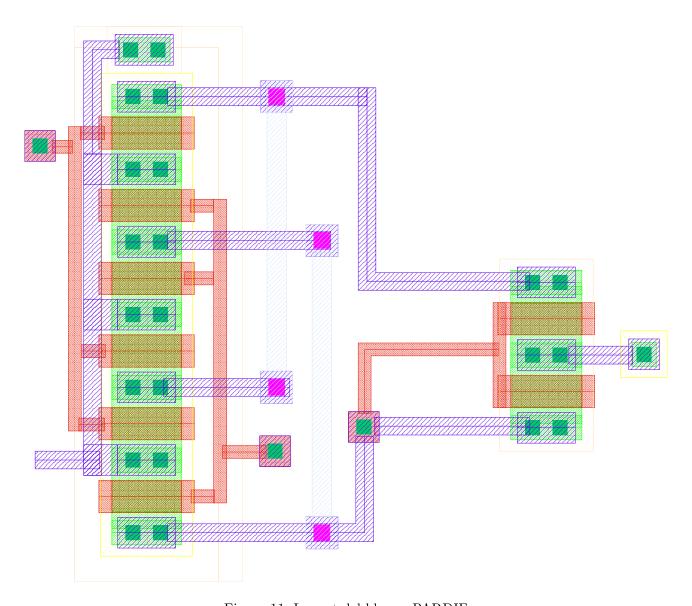

### 4.2. Simulación física del bloque PARDIF

El layout de este bloque se muestra en la Figura 11 y los resultados de los análisis en alterna y transitorio en la Figura 5. La descomposición en transistores unitarios (TUs) es la siguiente:

- T1 mide 12.9um, 3 TUs de 4.3um

- T2 mide 12.9um, 3 TUs

T1 y T2 están entrelazados. T3 y T4 comparten la puerta y el surtidor, T3 está conectado como diodo.

Figura 4: Simulación tras sustituir el bloque FUENTE

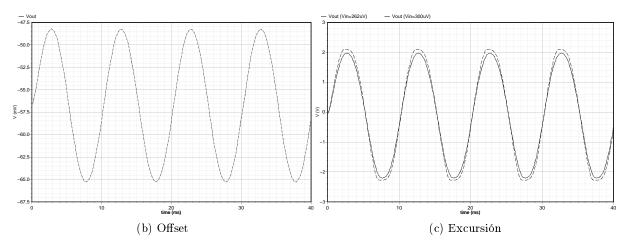

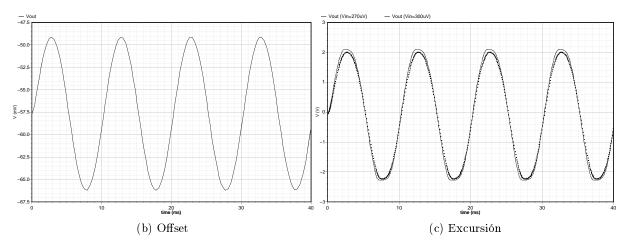

### 4.3. Simulación física del bloque SALIDA

El layout de este bloque se muestra en la Figura 12 y los resultados de los análisis en alterna y transitorio en la Figura 6. La descomposición en transistores unitarios (TUs) es la siguiente:

■ T6 mide 126um (después de corregido), 20 TUs de 6.3um

El condensador  $C_c$  tiene señuelos para evitar el efecto de vecindad en el atacado de las capas POLY11 y POLY2

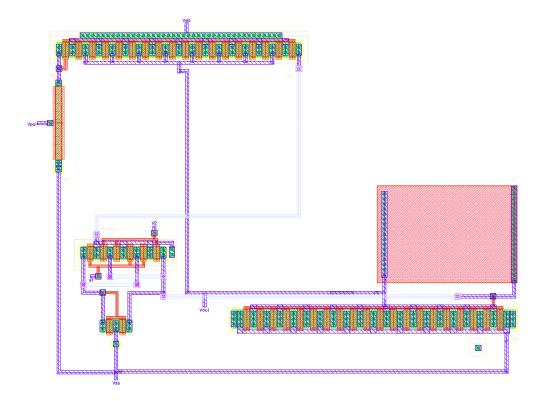

#### 4.4. Simulación física del layout

Ahora creamos un nuevo layout para el bloque MILLER que es la interconexión de los tres layouts anteriores, obtenemos su modelo analog\_extracted y hacemos una simulación del conjunto total.

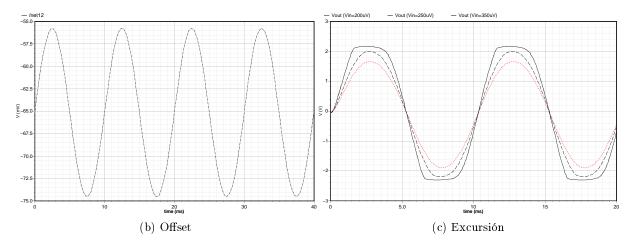

El layout de se muestra en la Figura 10 y los resultados de los análisis transitorio y alterna en la Figura 7

Figura 5: Simulación tras sustituir el bloque PARDIF

## A. Estudio de una fuente de corriente CMOS

En la fuente de corriente CMOS de la Figura 8, el transitor  $T_5$  está en saturación  $^2$  y su corriente es

$$I_{d5} = \frac{K_p'}{2} \frac{W_5}{L_5} (V_{gs5} - V_{th5})^2 (1 + \lambda V_{ds5})$$

(11)

si R=0, entonces  $V_{ds5}=5$ V y la corriente de salida es máxima, sustituyendo los valores  $\frac{K_p'}{2}\frac{W_5}{L_5}=248.397\frac{\text{uA}}{\text{V}^2},\ V_{gs5}=-1.386$ V,  $V_{th5}=-0.78$ V,  $V_{ds5}=5$ V y  $\lambda=\frac{1}{V_{EP}L_5}=0.0417$ V $^{-1}$  tenemos que  $I_{d5max}=I_{d5}\big|_{R=0}=110.42$ uA. También podriamos haber calculado esta corriente usando  $I_F$  y la relación de areas entre  $T_5$  y  $T_8$

Si consideramos  $T_5$  con  $\lambda=0$ , este se comporta como una fuente de corriente ideal:  $I_{d5}$  no depende de  $V_{ds5}$  y por tanto no depende de la R de carga que conectemos siempre y cuando  $V_{ds}$  sea suficiente para mantener a  $T_5$  en saturación. En el límite de saturación se cumple  $V_{ds5}=V_{ds5min}=V_{gs5}-V_{th5}=V_{ds5min}$

$<sup>^2</sup>$ Siempre que la R de carga sea suficientemente pequeña como para mantener a  $T_5$  en saturación

Figura 6: Simulación tras sustituir el bloque SALIDA

-0.61V. Esto nos da una carga máxima absoluta aproximada (hemos considerado  $\lambda = 0$ ) de

$$R_{max} = \frac{V_{dd} - V_{ss} + V_{ds5min}}{I_{d5max}} \approx 38k$$

(12)

si ahora consideramos el efecto de modulación del canal  $(\lambda \neq 0)$ , vemos que a medida que incrementamos R la corriente  $I_{d5}$  disminuye porque depende de  $V_{ds5}$  y este depende a se vez de R. La corriente máxima  $I_{d5max}$  se tiene sólo cuando R=0, para una  $R\neq 0$  la corriente de salida es

$$I_{d5} = \underbrace{\frac{K'_p}{2} \frac{W_5}{L_5} (V_{gs5} - V_{th5})^2}_{a} (1 + \lambda (V_{cc} - I_{d5}R))$$

$$I_{d5} = a - \lambda a I_{d5}R + \lambda a V_{cc}$$

$$I_{d5} = \frac{a(1 + \lambda V_{cc})}{1 + \lambda a R}$$

$$I_{d5} = \frac{I_{d5max}}{1 + \lambda a R}$$

(13)

Figura 7: Offset y excursión en la simulación de conjunto

Para determinar la carga máxima admisible podemos definir el concepto de error relativo  $\epsilon$  en la corriente de salida como

$$\epsilon = \frac{I_{d5max} - I_{d5}}{I_{d5}} = \frac{\Delta I_{d5}}{I_{d5}} \tag{14}$$

sustituyendo en esta ecuación la expresión (13) y desarrollando podemos poner  $\epsilon$  en función de la R de carga

$$\epsilon = \frac{\Delta I_{d5}}{I_{d5}} = \lambda aR \tag{15}$$

la R máxima de carga en función del error relativo  $\epsilon$  admitido es entonces

$$R < \frac{\epsilon}{\lambda a}$$

$T_5 \text{ saturado } (R << R_{max})$  (16)

la Tabla 3 muestra la R máxima admisible para los disintos  $\epsilon$ , obtenida con la ecuación (16)

La Figura 9 muestra los resultados de simulación de la fuente de corriente. Podemos ver que la corriente  $I_{d5max}$  es mayor que la calculada teoricamente y que la carga máxima absoluta es R=33k.

| $\epsilon$ | R máxima (KOhm) |

|------------|-----------------|

| < 1 %      | 2.63            |

| <3%        | 7.89            |

| <5%        | 13.15           |

| < 7 %      | 18.40           |

| < 10 %     | 26.29           |

Cuadro 3: R máxima en función del error relativo  $\epsilon$  permitido

Figura 8: Esquema de una fuente de corriente CMOS

Para esta carga la curva de  $I_{d5}$  presenta un codo que corresponde al punto en el que  $T_5$  pasa de saturación a óhmnica, también se puede ver que la ecuación (16) es correcta.

POR EJEMPLO: para R = 33KOhm:

- $\epsilon$ teórico Usando la ecuación 16],  $\epsilon = Ra\lambda = 12.1\,\%$

- $\epsilon$ real Usando la Figura 9],  $\Delta I_{d5}=151-136=15 \mathrm{uA} \Rightarrow \epsilon=15/136=11\,\%$

Figura 9:  $I_{d5}$  en función de la carga

Figura 10: Layout del bloque FUENTE, con señuelos en los laterales

Figura 11: Layout del bloque PARDIF

Figura 12: Layout del bloque SALIDA

$Figura\ 13:\ Layout\ del\ OTA-Miller\ formado\ por\ la\ interconexi\'on\ de\ los\ 3\ layouts\ anteriores\ (no\ optimizado)$